The DARE consortium has been selected to implement a Framework Partnership Agreement (FPA) for developing a large-scale European initiative for a HPC ecosystem based on RISC-V. The FPA will run for six years, until 2030.

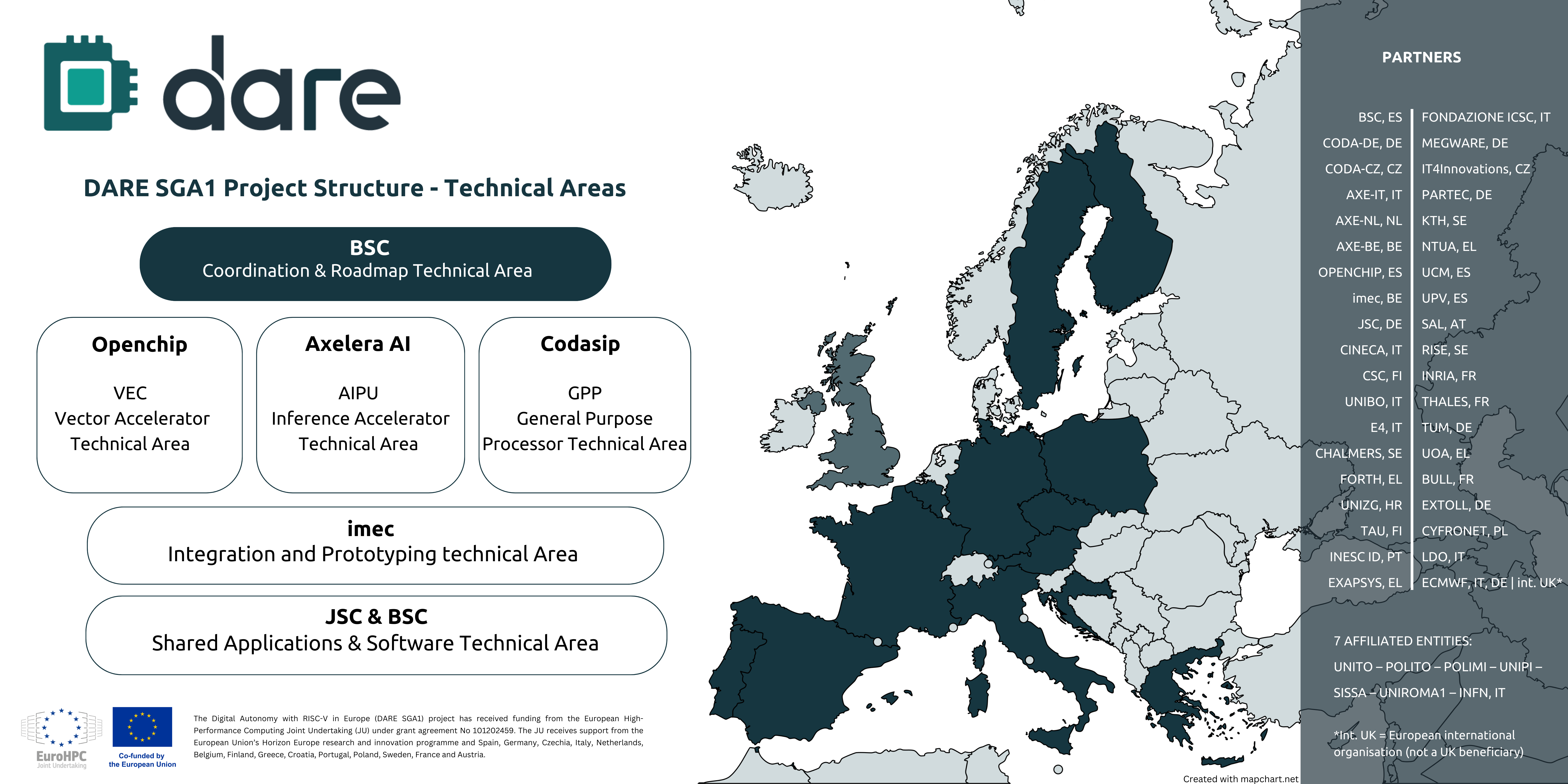

The DARE project is the first Specific Grant Agreement (SGA) for the development of European microprocessors based on RISC-V and cutting edge chiplet technology. It will design, develop, and tape-out in advanced CMOS technology nodes one processor, and two accelerators based on the open RISC-V instruction set architecture. These three components will overcome the limitations of traditional monolithic chips because of their scalability, cost, power, and efficiency trade-off, enabling the creation of truly European products in advanced nodes that aim to power future EuroHPC supercomputers. More precisely, the project will start by designing and developing:

- A general-purpose processor (GPP) optimised for HPC workloads

- A vector accelerator (VEC) for high-precision HPC and emerging applications in the HPC-AI convergence domain;

- An AI Processing Unit (AIPU) designed for AI inference acceleration in HPC applications;

- A supercomputing hardware (HW)/software (SW) stack for HPC and AI

38 partners from 13 countries including SMEs will collaborate as a consortium coordinated by the Barcelona Supercomputing Centre (BSC) to build European cutting-edge HPC hardware and software.

Building on research from EuroHPC JU-funded projects such as the European Processor Initiative (EPI), MEEP, eProcessor, EUPILOT, and EUPEX, DARE is part of the broad European Union's strategy to reach European autonomy in strategic hardware technologies by investing and building a diverse technology portfolio including processors, (AI) accelerators, quantum chips and other state of the art hardware components.

- Project duration

- 1 Mar 2025 - 28 Feb 2030

- Project locations

- Barcelona, Spain

- Overall budget

- €240 000 000

- Project website

- https://dare-riscv.eu/home/

Stakeholders

Coordinators

Barcelona Supercomputing Center (BSC)

- Address

- Barcelona, Spain

- Website

- https://www.bsc.es/

Participants

Codasip

- Address

- Germany

- Website

- https://codasip.com/

Axelera

- Address

- Netherlands

- Website

- https://www.axelera.ai/

Openchip

- Address

- Spain

- Website

- https://openchip.com/

Interuniversitair Micro-Electronica Centrum (Imec)

- Address

- Belgium

- Website

- https://www.imec-int.com/en

Forschungszentrum Jülich

- Address

- Germany

- Website

- https://www.fz-juelich.de/

Cineca

- Address

- Italy

- Website

- https://www.cineca.it/it

CSC

- Address

- Finland

- Website

- https://csc.fi/

Alma Mater Studiorum - Università di Bologna

- Address

- Italy

- Website

- https://www.unibo.it/it

E4 Computer Engineering SpA

- Address

- Italy

- Website

- https://www.e4company.com/en/

Chalmers tekniska högskola

- Address

- Sweden

- Website

- https://www.chalmers.se/en/

Foundation for Research and Technology - Hellas

- Address

- Greece

- Website

- https://www.forth.gr/

Fakultet elektrotehnike i računarstva (UNIZG)

- Address

- Croatia

- Website

- https://www.fer.unizg.hr/

Tampereen korkeakoulusäätiö sr (TAU)

- Address

- Finland

- Website

- https://www.tuni.fi/en

Instituto de Engenharia de Sistemas e Computadores - Investigação e Desenvolvimento ( INESC ID )

- Address

- Portugal

- Website

- https://www.inesc-id.pt/

️Exascale Performance Systems - Exapsys IKE

- Address

- Greece

- Website

- https://exapsys.eu/

Centro Nazionale di Ricerca in High Performance Computing, Big Data e Quantum Computing (FONDAZIONE ICSC)

- Address

- Italy

- Website

- https://www.supercomputing-icsc.it/en

Università degli Studi di Torino

- Address

- Italy

- Website

- https://www.unito.it/

Politecnico di Torino

- Address

- Italy

- Website

- https://www.polito.it/

Politecnico di Milano

- Address

- Italy

- Website

- https://www.polimi.it/

Università di Pisa

- Address

- Italy

- Website

- https://www.unipi.it/

Scuola Internazionale Superiore di Studi Avanzati

- Address

- Italy

- Website

- https://www.sissa.it/it

Universita' Degli Studi Di Roma La Sapienza

Istituto Nazionale di Fisica Nucleare (INFN )

- Address

- Italy

- Website

- https://www.infn.it/

MEGWARE Computer Vertrieb und Service GmbH

- Address

- Germany

- Website

- https://www.megware.com/

VSB - Technical University of Ostrava

- Address

- Czechia

- Website

- https://www.vsb.cz/en

ParTec AG

- Address

- Germany

- Website

- https://par-tec.com/

Kungliga Tekniska högskolan

- Address

- Sweden

- Website

- https://www.kth.se/

Erevnitiko Panepistimiako Institouto Systimaton Epikoinonion kai Ypologiston (NTUA)

- Address

- Greece

- Website

- https://www.ntua.gr/en/

Universidad Complutense de Madrid

- Address

- Spain

- Website

- https://www.ucm.es/

Universitat Politècnica de València (UPV)

- Address

- Spain

- Website

- https://www.upv.es/index-en.html

European Centre for Medium-Range Weather Forecasts (ECMWF)

- Address

- United Kingdom

- Website

- https://www.ecmwf.int/

Swedish research creating sustainable growth (RISE)

- Address

- Sweden

- Website

- https://www.ri.se/en

Institut national de recherche en informatique et en automatique (INRIA)

- Address

- France

- Website

- https://inria.fr/

Thales

- Address

- France

- Website

- https://www.thalesgroup.com/fr/marches/defense-et-securite/activites-services-n…

Technische Universitaet Muenchen (TUM)

- Address

- Germany

- Website

- https://www.cit.tum.de/en/cit/home/

National and Kapodistrian University of Athens (UOA)

- Address

- Greece

- Website

- https://en.uoa.gr/

Atos

- Address

- France

- Website

- https://atos.net/en/?utm_source=www.bull.com%2F&utm_medium=301

Extoll

- Address

- Germany

- Website

- https://www.extoll.com/

Akademia Górniczo-Hutnicza im. Stanisława Staszica w Krakowie (CYFRONET)

- Address

- Poland

- Website

- https://www.cyfronet.pl/

Leonardo - Societa per Azioni

- Address

- Italy

- Website

- https://www.leonardo.com/it/home

Silicon Austria Labs (SAL)

- Address

- Austria

- Website

- https://silicon-austria-labs.com/en/